热搜关键词: 老化板定制 BGA测试座 芯片老化板 IC测试座定制

BGA(Ball Grid Array,球栅阵列)封装是一种以底部锡球阵列为引脚的芯片封装技术,相较于传统QFP(四方扁平封装)等形式,其核心优势在于解决

“高引脚密度与小型化” 的矛盾,结构特点与核心价值如下:

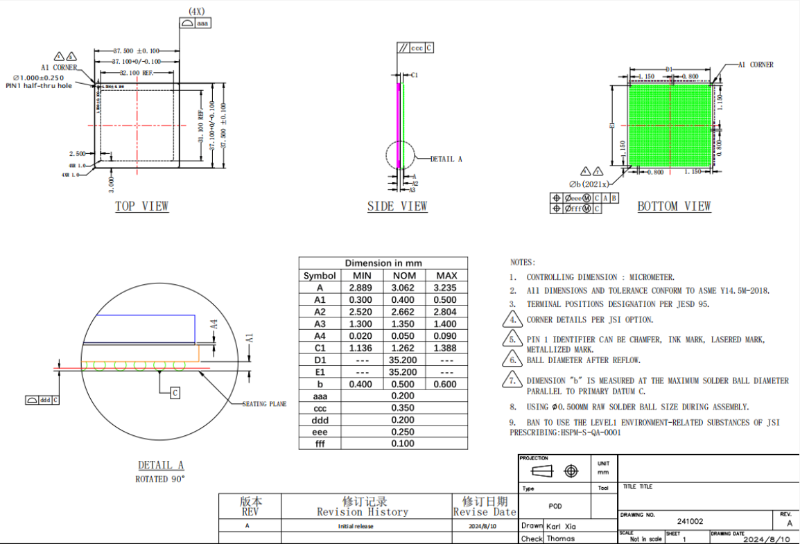

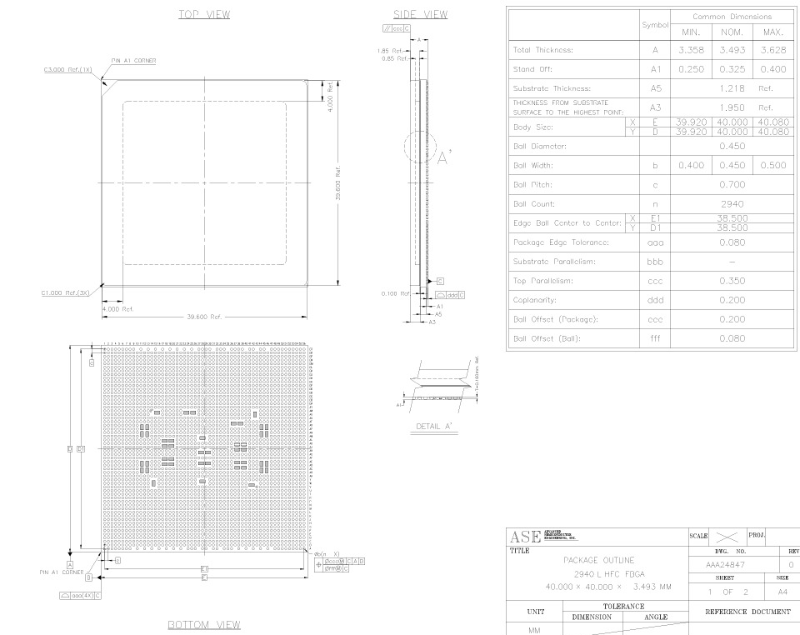

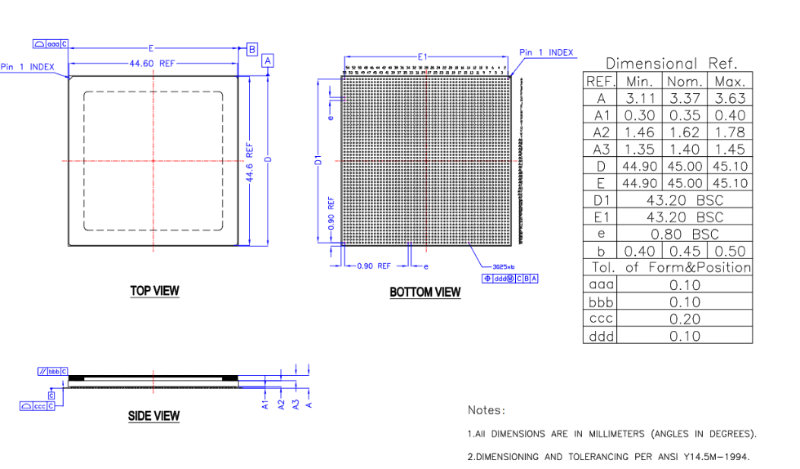

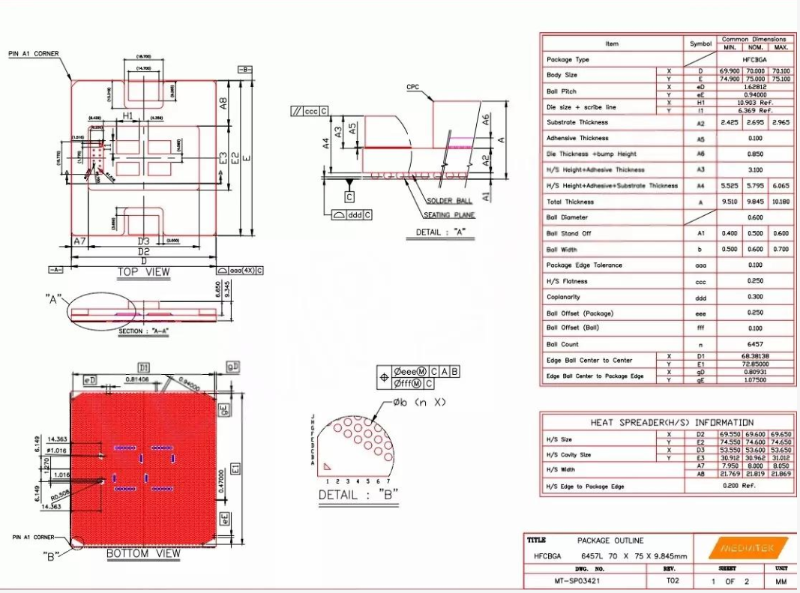

结构设计:芯片底部均匀分布圆形锡球(直径通常0.3-0.8mm

),通过锡球与 PCB 板上的焊盘焊接实现电气连接,无需外露引脚,封装体积较同引脚数 QFP 缩小

40% 以上;

性能优势:锡球阵列布局缩短信号路径,寄生电感

≤5nH、寄生电容≤2pF,高频信号传输损耗降低 30%(适配 1GHz 以上芯片);底部裸露焊盘可直接接触 PCB 散热,散热效率较 QFP 提升 50% ,适配高功率芯片(如 CPU、电源管理芯片);

可靠性提升:锡球具备一定弹性,可吸收PCB 热膨胀产生的应力,减少焊点开裂风险,长期工作可靠性(MTBF)较传统封装提升 2-3 倍。

BGA 封装因 “高集成度、低信号损耗、强散热” 特性,广泛应用于高引脚需求、高频 / 高功率、小型化要求高的领域:

消费电子领域:智能手机SoC

(如骁龙 8 Gen3,采用 BGA256 封装)、平板电脑 CPU (苹果 A17 Pro,BGA338)、笔记本电脑显卡(NVIDIA MX550 ,BGA192 ),需兼顾小尺寸与高性能;

工业控制领域:PLC

(可编程逻辑控制器)核心芯片(如西门子 S7-1200,BGA77)、工业传感器信号处理芯片(

BGA49),需耐受 - 40℃~85℃宽温,且抗振动;

汽车电子领域:车载MCU

(如英飞凌 AURIX,BGA144)、自动驾驶雷达芯片(77GHz 毫米波芯片, BGA121),需满足车规级可靠性(高温 125℃、低温 - 40℃ );

航空航天与医疗领域:卫星通信芯片(BGA216 ,抗辐射)、医疗影像设备信号处理芯片(BGA196,高稳定性),需极端环境下的长期稳定运行。

BGA 封装的 “pin 脚” 即底部锡球数量,不同锡球数(pin 数)与间距适配不同集成度需求,主流型号及参数如下:

|

BGA 封装型号 |

锡球数量(pin) |

锡球间距 |

封装尺寸(长 × 宽) |

核心特点 |

典型应用 |

|

BGA25 |

25 |

1.0mm |

5mm×5mm |

超小型,低引脚密度 |

可穿戴设备电源管理芯片 |

|

BGA49 |

49 |

0.8mm |

6mm×6mm |

平衡尺寸与集成度 |

物联网传感器芯片 |

|

BGA77 |

77 |

0.8mm |

8mm×8mm |

中低集成度,散热性好 |

工业控制 MCU |

|

BGA144 |

144 |

0.5-0.8mm |

10mm×10mm |

高集成度,多信号通道 |

车载雷达前端芯片 |

|

BGA216 |

216 |

0.5mm |

12mm×12mm |

超高集成度,高频适配 |

5G 基站信号处理芯片 |

|

BGA338 |

338 |

0.4mm |

15mm×15mm |

极高引脚密度,超小间距 |

高端智能手机 SoC |

|

注:锡球间距越小(如 0.4mm),对焊接精度、测试座接触可靠性要求越高 |

|

|

|

|

|

不同封装形式在引脚结构、性能优势上差异显著,具体对比如下:

|

封装类型 |

引脚形式 |

核心优势 |

核心劣势 |

适用场景 |

|

BGA |

底部锡球阵列 |

高引脚密度、低寄生参数、散热好 |

维修难度高(需热风枪返修) |

中高端芯片(CPU、SoC、射频芯片) |

|

FBGA |

细间距锡球阵列(间距≤0.5mm) |

超小封装尺寸、更高引脚密度(如 FBGA338) |

焊接良率对工艺要求极高 |

微型消费电子(智能手表、蓝牙耳机) |

|

UBGA |

超小尺寸锡球阵列(封装≤5mm×5mm) |

极致小型化(如 UBGA25,4mm×4mm) |

功率承载能力低(≤2W) |

微型传感器、低功耗 IoT 芯片 |

|

MBGA |

金属外壳 + 锡球阵列 |

抗电磁干扰(EMI)、抗振动 |

封装成本高、体积略大 |

汽车电子、工业控制高可靠性芯片 |

|

PGA |

底部插针阵列(引脚外露) |

接触可靠性高、维修便捷(可插拔) |

体积大、引脚密度低(≤200pin) |

早期 CPU、服务器芯片 |

|

LGA |

底部金属焊盘阵列(无锡球) |

无铅环保、焊接应力小 |

需 PCB 对应焊盘,测试需专用探针座 |

高端 CPU(如 Intel 酷睿)、FPGA |

BGA 芯片测试需覆盖 “电气连接可靠性、长期工作稳定性、封装结构完整性” 三大维度,核心测试体系如下:

电性能与接触可靠性测试

接触电阻:锡球与测试座 / PCB 的导通电阻(要求

≤50mΩ,避免信号衰减);

绝缘电阻:相邻锡球间的绝缘能力(高温高湿下≥100MΩ

,防短路);

引脚开路 / 短路检测:排查锡球虚焊、连锡(如

BGA144 需 100% 检测所有引脚通路);

高频信号传输:测试 1GHz 以上信号的插入损耗(

≤0.5dB)、相位偏移(≤5°),验证信号完整性。

可靠性测试

高温工作寿命(HTOL):

125℃/150℃下带载运行 1000-2000 小时(车规 125℃/2000 小时),无性能衰减;

温度循环测试:-40℃~125℃循环

1000 次(工业 500 次),每次循环 1 小时,测试后焊点无开裂;

湿热测试:40℃、

90% RH 环境下放置 1000 小时,绝缘电阻保持≥10MΩ,无锡球腐蚀;

机械冲击测试:1500g 加速度、

0.5ms 脉冲冲击,模拟运输 / 跌落,封装无脱落。

封装完整性测试

焊球剪切力:用推拉力测试机施加垂直力,单个锡球剪切力≥6gf

(0.8mm 间距),避免焊球脱落;

封装空洞检测:超声扫描(C-SAM)检测锡球与芯片间的空洞率(

≤15%),空洞过大会导致散热不良;

外壳密封性:氦质谱检漏,漏率≤1×10⁻⁸ atm

・cm³/s,防潮气侵入。

接触可靠性测试

接触电阻:用微欧姆计(如 Keithley 2450)连接测试座探针与锡球,施加

100mA 测试电流,读取电阻值;

开路 / 短路:用

ICT(在线测试仪)搭建测试回路,逐一检测每个锡球的通路状态,短路则报警。

可靠性测试

高温老化:将 BGA 芯片安装在测试座上,一同放入温度箱(精度

±1℃),施加额定电压 / 电流,每隔 24 小时记录性能参数;

温度循环:采用高低温箱(-40℃~125℃),升温

/ 降温速率≤5℃/min,循环后用光学显微镜观察焊点状态;

焊球剪切:用推拉力测试机(如 DAGE 4000)的剪切刀,沿平行于芯片表面方向施加力,记录剪切力值。

封装完整性测试

超声扫描(C-SAM):用

20-50MHz 超声波探头扫描芯片底部,空洞区域因声波反射差异显示为黑色,计算空洞面积占比;

氦质谱检漏:将芯片密封后充入氦气,放入检漏仪真空室,检测泄漏的氦气浓度,换算漏率。

测试环境控制

屏蔽室:测试高频信号时,需在屏蔽效能≥80dB@1GHz

的屏蔽室中进行,避免电磁干扰;

防静电环境:测试全程保持 ESD 防护(静电电压 ≤100V),防止静电击穿芯片引脚。

|

标准体系 |

核心规范编号 / 名称 |

关键要求 |

适用测试项目 |

|

JEDEC(美国) |

JESD22-A108(HTOL) |

工业级:125℃/1000 小时;车规级:150℃/2000 小时,性能衰减≤10% |

高温工作寿命 |

|

JEDEC |

JESD22-B104(温度循环) |

-40℃~125℃循环 1000 次,每次高低温停留 30 分钟,焊点无开裂 |

温度循环可靠性 |

|

IPC(国际) |

IPC-9701(焊点性能) |

焊球剪切力:0.8mm 间距≥6gf,0.5mm 间距≥4gf;空洞率≤15% |

封装完整性(焊球、空洞) |

|

AEC(车规) |

AEC-Q100 Grade 0 |

车规最高等级:工作温度 - 40℃~150℃,HTOL 150℃/2000 小时,无性能失效 |

汽车电子 BGA 芯片可靠性 |

|

MIL-STD(军规) |

MIL-STD-883H Method 2002.1 |

焊球剪切力测试:施加力速率 100μm/s,记录最小剪切力值,无焊球脱落 |

军规 BGA 芯片封装强度 |

|

GB(中国) |

GB/T 4937.1-2018 |

等同 IEC 标准,绝缘电阻测试:500V DC 下≥100MΩ,湿热后≥10MΩ |

绝缘可靠性 |

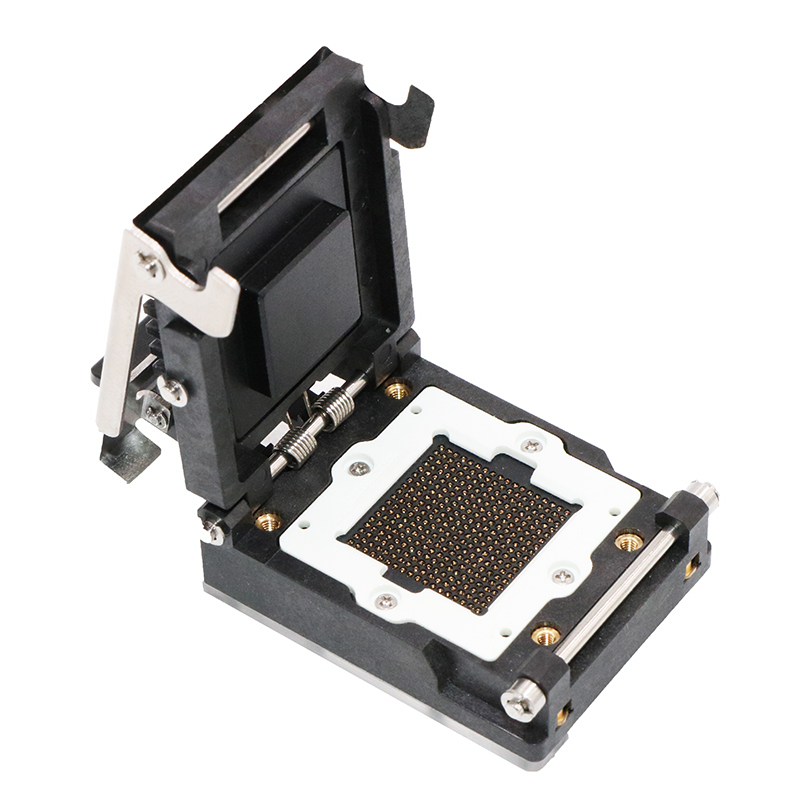

BGA 芯片测试的核心痛点是 “锡球间距小(最小 0.4mm)、高温环境下接触不可靠、多引脚同步测试难”,鸿怡电子测试座通过针对性设计解决这些痛点,关键作用体现在五大维度:

高精度接触,保障测试可靠性

采用 “

弹性探针阵列” 设计,探针直径最小 0.15mm,定位精度 ±0.02mm

,适配 BGA25-BGA338 全系列封装(0.4-1.0mm 间距),确保每个锡球与探针精准接触,接触电阻≤30mΩ

,避免因接触不良导致的开路 / 短路误判;

探针采用镀金银合金材质(镀层厚度≥5μm

),插拔寿命≥5 万次,磨损率降低 50%,长期测试后仍保持稳定接触。

宽温耐受,支持可靠性测试

座体采用耐高温 LCP 工程塑料(耐温

- 55℃~150℃),探针选用耐温铍铜材质,可随芯片一同放入温度箱,满足 125℃高温老化、-40℃~125℃温度循环测试,长期测试无材质变形、探针氧化;

底部设散热通道,与 BGA 芯片裸露焊盘紧密贴合,散热效率提升

40%,避免高功率芯片(如 20W CPU)测试时因温升导致的性能漂移。

多工位并行,提升测试效率

支持 8-32 路并行测试,

一拖多工位可同时测试多颗 BGA 芯片(如

16 路 BGA144),测试效率较传统单工位提升 16 倍;

集成 ATE 自动测试系统接口(

GPIB/LAN),可实时采集接触电阻、绝缘电阻、高频信号参数,自动生成测试报告,减少人工干预,误判率降至 0.1% 以下。

高频信号优化,保障测试精度

座体内部采用 “

短路径布线”,射频通路长度≤3mm,寄生电感≤2nH、寄生电容

≤0.3pF,适配 1GHz 以上高频芯片测试,插入损耗≤0.3dB,相位偏移

≤3°,确保高频信号传输完整性;

内置电磁屏蔽腔(屏蔽效能≥85dB@1GHz

),隔离外界电磁干扰,避免高频测试时的信号串扰,使相位偏移测试误差从 ±2° 降至 ±0.5°。

灵活适配与便捷操作

采用 “

快拆式探针模组” 设计,更换不同 BGA 型号时无需更换整个测试座,仅需更换探针模组(耗时≤5

分钟),适配成本降低 60%;

顶部设真空吸装置,芯片自动定位固定,拆装无需工具,单颗芯片更换时间≤10 秒,降低测试人员操作强度。

随着 BGA 封装向 “超密间距(0.3mm)、3D 堆叠(如 3D BGA)” 演进,测试座面临 “探针密度更高、多芯片同步测试” 的挑战。鸿怡电子正研发 “3D BGA 测试座”(支持堆叠芯片的多层面测试)与 “智能校准测试座”(集成温度传感器与阻抗补偿模块),实时修正测试偏差,为下一代超密间距 BGA 芯片的量产测试提供技术支撑。

【本文标签】 鸿怡芯片测试方案:BGA芯片封装?BGA芯片测试?BGA芯片测试座

【责任编辑】