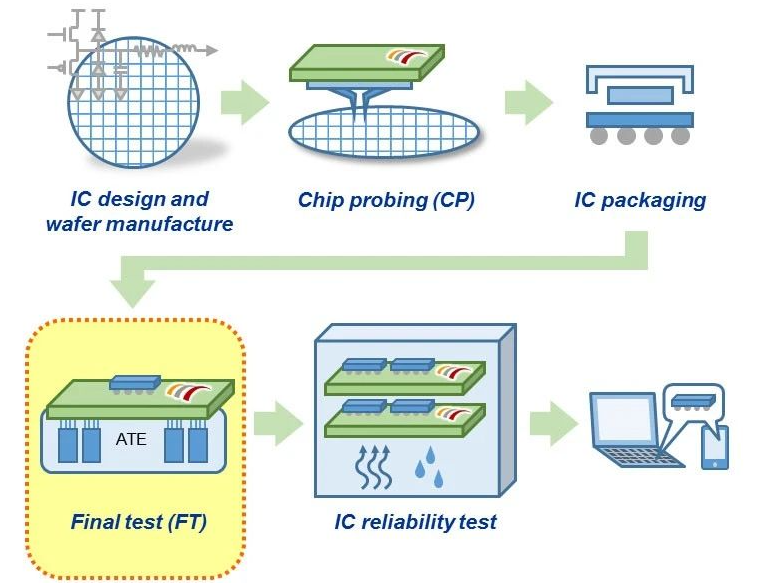

在半导体芯片从设计到量产的全流程中,芯片测试座的评估与测试是不可或缺的关键环节,其核心价值体现在以下几个方面:

一、设计验证阶段:确保功能与性能达标

1. 原型功能验证

在芯片设计初期,工程师通过测试座连接原型芯片与测试设备,验证其逻辑功能是否符合设计预期。例如,使用Socket Phone等治具快速完成芯片的开机测试和固件烧录,避免反复焊接对芯片造成损伤。对于高频芯片(如5G基带芯片),测试座需支持27GHz以上的信号频率,并通过阻抗匹配(±3%)和低插损(<2dB)设计确保信号完整性,防止因测试设备引入的干扰导致误判。

2. 极端条件测试

测试座需模拟芯片在极端温度(-65℃~200℃)、电压等环境下的表现。例如,车规级芯片需通过高温反向偏压(HTRB)测试评估长期稳定性,测试座的热管理设计(如散热片、导热硅胶)直接影响测试结果的可靠性。

3. 参数精确测量

对于分立器件(如MOSFET、IGBT),测试座需采用四线制开尔文连接法,消除接触电阻对微欧级Rds(on)测量的干扰,确保动态参数(如栅极电荷Qg)的准确性,为驱动电路设计提供依据。

二、晶圆测试阶段:早期缺陷筛选与良率提升

1. 晶圆级并行测试

晶圆测试座通过探针卡与晶圆上的裸芯片(Die)接触,一次可对多个芯片进行并行测试。例如,探针卡采用钨铜合金或镀金探针,接触阻抗≤15mΩ,支持0.35mm间距焊球的检测,实现微米级精度的电气连接。测试结果实时生成晶圆Map图,标记合格与缺陷芯片,避免后续封装环节的成本浪费。

2. 功能与可靠性预验证

晶圆测试不仅检测芯片的基本功能(如逻辑门响应),还通过IDDQ测试检测桥接、短路等物理缺陷。例如,CMOS电路的静态漏电测试(IDD测试)可识别潜在的可靠性风险,确保封装前剔除不良品。

3. 参数分级与优化

根据测试结果,芯片可按性能分级(如速度、功耗),适配不同市场需求。例如,高频测试座支持40GHz信号传输,寄生电感<0.1nH,可精准筛选出满足PCIe 5.0协议的芯片,提升产品附加值。

三、封装与量产阶段:确保产品一致性与可靠性

1. 封装后全功能测试

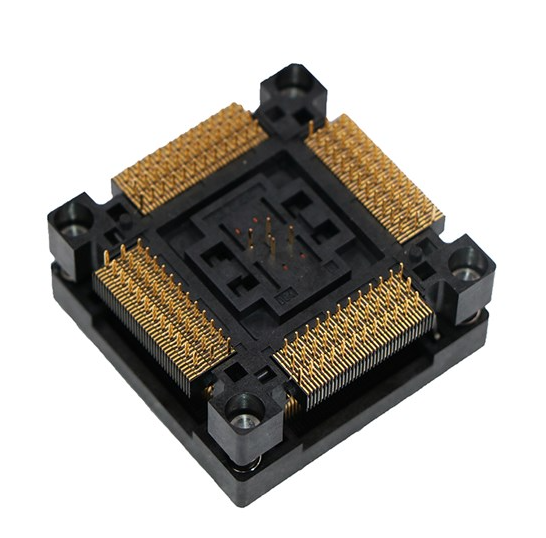

封装后的芯片通过测试座连接测试机,进行全功能验证。例如,DDR内存测试夹具集成IBIS模型仿真功能,可预判信号完整性风险,确保DDR5-6400颗粒的读写稳定性。对于BGA封装芯片,测试座采用双曲面接触头设计,接触电阻<20mΩ,适配eMMC、LPDDR等复杂封装形式。

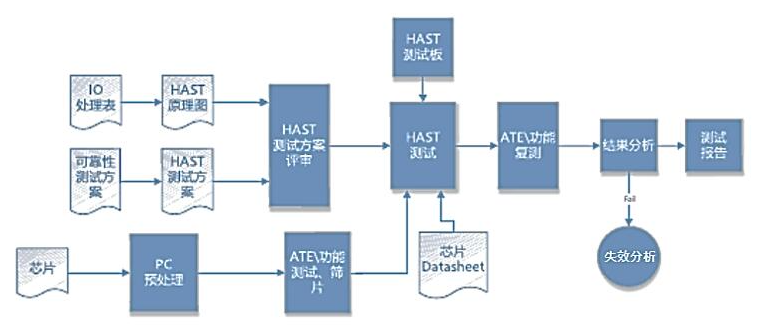

2. 高温老化与可靠性筛选

量产前的高温老化测试(如168小时持续运行)通过老化座施加额定电压/电流,模拟长期使用场景,筛选早期失效器件。多工位并行测试(如64工位老化板)可将单颗测试成本降低30%以上。

3. 自动化与效率提升

测试座与自动测试设备(ATE)集成,实现从晶圆测试到成品测试的全流程自动化。例如,晶圆级测试座支持与探针台、测试机的实时通信,测试效率提升至单日10万颗以上。

四、全流程质量控制:降低风险与成本

1. 早期问题定位

在设计阶段通过测试座发现的问题(如信号时序偏移),可及时优化电路设计,避免量产阶段的大规模返工。例如,JTAG边界扫描技术通过测试座实现芯片内部节点的远程诊断,快速定位制造缺陷。

2. 测试座选型与优化

测试座的设计需综合考虑封装兼容性、频率支持、耐久性等因素。例如,BGA封装芯片需专用探针座,而射频芯片测试座需采用同轴结构屏蔽高频干扰。不合理的测试座选择可能导致测试覆盖率不足,增加漏检风险。

3. 行业标准与合规性

车规级芯片测试需满足ISO 26262功能安全要求,测试座需通过认证的测试流程(如多物理场耦合测试),确保在电-热-力综合作用下参数无漂移。

五、技术挑战与创新方向

1. 高频与高速信号处理

随着5G和AI芯片的发展,测试座需支持100GHz以上的信号频率,并通过TDR(时域反射计)实时监测传输线阻抗,确保眼图余量≥0.3UI。

2. 多物理场协同测试

宽禁带器件(如SiC、GaN)的测试需同步监测电、热、力参数,测试座需集成实时补偿算法,消除多物理场耦合引起的误差。

3. 智能化与AI集成

未来测试座可能嵌入AI算法,实现参数自适应调整和故障预测。例如,通过机器学习分析测试数据,提前预判芯片寿命和潜在失效模式。

芯片测试座作为连接芯片与测试设备的桥梁,贯穿设计验证、晶圆测试、封装测试到量产的全流程。其核心作用不仅在于检测芯片的功能与性能,更在于通过早期缺陷筛选、参数优化和可靠性验证,确保产品质量、降低成本,并推动半导体技术的持续创新。随着芯片技术向高频、高集成度发展,测试座的设计与应用将成为决定产业竞争力的关键因素之一。