一、DDR存储芯片类型与特点

1. DRAM(动态随机存取存储器)

核心特点:基于电容电荷存储数据(1T1C结构),需定期刷新(64ms周期),密度高、成本低,用于主存。例如,DDR5-6400颗粒带宽达51.2GB/s,采用PRAC(逐行激活计数)技术防止过度激活。

技术演进:

DDR4支持1.2V电压,DDR5引入400MHz基频、PAM4调制,单颗芯片容量达16Gb。

2. SRAM(静态随机存取存储器)

核心特点:基于触发器(6T/8T结构),无需刷新,速度快(1-10ns访问时间)、功耗高,用于高速缓存。例如,L2/L3缓存采用SRAM实现低延迟数据存取。

关键参数:访问时间(TAA≤12ns)、静态电流(ISB≤10μA)、动态电流(ICC≤50mA)。

3. NAND闪存

核心特点:

非易失性存储,浮栅晶体管结构,支持块擦除(4-128KB),用于SSD和嵌入式存储。例如,3D TLC NAND层数超200层,单Die容量达1Tb。

接口标准:ONFI 4.1支持DDR400接口(800MT/s),Toggle DDR 2.0带宽达400MB/s。

4. DIMM(双列直插内存模块)

核心特点:

将多颗DRAM芯片集成于PCB,通过金手指与主板连接。例如,DDR4 DIMM支持RDIMM/LRDIMM架构,容量达128GB。

标准化设计:

JEDEC规定DIMM物理尺寸(如UDIMM长133.35mm)和信号定义(如DDR4采用284针接口)。

5. LOGIC芯片(内存控制器/PHY)

核心特点:

负责DRAM时序控制、信号调理和协议转换。例如,DDR5 PHY集成PLL(锁相环)实现4800MT/s数据速率。

关键功能:

支持Gear Down Mode(GDM)降低功耗,集成ODT(片上终端)优化信号完整性。

二、测试项、参数与标准

1. DRAM测试

功能测试:

读写验证:全0/全1/棋盘格模式,误码率(BER)≤1e-16。

刷新测试:64ms刷新周期内,单颗芯片刷新次数≥8192次。

时序参数:

tRCD:行激活到列选通延迟(DDR4典型值15-30ns)。

tCL:CAS潜伏期(DDR5-6400对应CL=32)。

tREFI:刷新间隔(DDR4为7.8μs)。

信号完整性:

眼图测试:眼高≥0.3UI,眼宽≥0.2UI,抖动(TJ)≤50ps。

可靠性测试:

高温老化:85℃/168小时持续读写,数据保持率≥99.9%。

测试标准:JEDEC JESD79-4(DDR4)、JESD79-5C(DDR5)。

2. SRAM测试

功能测试:

固定型故障:检测Stuck-at-0/1、Transition Fault。

数据保持:断电后数据保持时间≥10年(典型值)。

时序参数:

TAA:地址到数据输出时间(SRAM VDSR32M32为12ns)。

TACS:片选到数据输出时间(≤10ns)。

电气参数:

VOH/VOL:输出高/低电平(3.3V器件VOH≥2.4V,VOL≤0.4V)。

测试标准:JEDEC JESD78B(SRAM通用规范)。

3. NAND闪存测试

功能测试:

块擦除:擦除时间≤1ms/块,坏块率≤0.01%。

ECC校验:LDPC纠错能力≥48bit/1KB,BER≤1e-15。

耐久性测试:

P/E周期:SLC≥10万次,QLC≥1000次。

接口参数:

tDQSS:DQS建立时间(ONFI 4.1要求0.75-1.25tCK)。

tCMD:命令周期时间(异步模式≤25ns)。

测试标准:ONFI 4.1、JEDEC JESD218(NAND接口规范)。

4. DIMM测试

模块级测试:

SPD校验:读取EEPROM中时序参数(如CAS Latency、tRCD),确保与JEDEC标准一致。

电源管理:VDDQ电压容差±5%,断电后残留电压≤0.1V。

信号完整性:

串扰测试:相邻引脚间串扰≤-20dB(1GHz)。

阻抗匹配:数据线差分阻抗100Ω±10%,地址线单端阻抗50Ω±10%。 测试标准:JEDEC JESD209-4(DDR4 DIMM)、JESD209-5(DDR5 DIMM)。

5. LOGIC芯片测试

协议合规性:

PCIe 5.0:支持128GT/s速率,通道误码率≤1e-12。

USB4:测试80Gbps信号眼图,抖动容限≥0.5UI。

时序控制:

时钟偏移:Fly-by拓扑下,tCLK skew≤±50ps。

ODT校准:DDR5 PHY的ODT值(40-60Ω)与JEDEC标准偏差≤5%。 功耗测试:

动态功耗:1.1V电压下,数据传输功耗≤50mW/Gbps。

测试标准:PCI-SIG PCIe 5.0 Base Specification、USB-IF USB4 Specification。

三、鸿怡存储芯片测试座解决方案关键应用

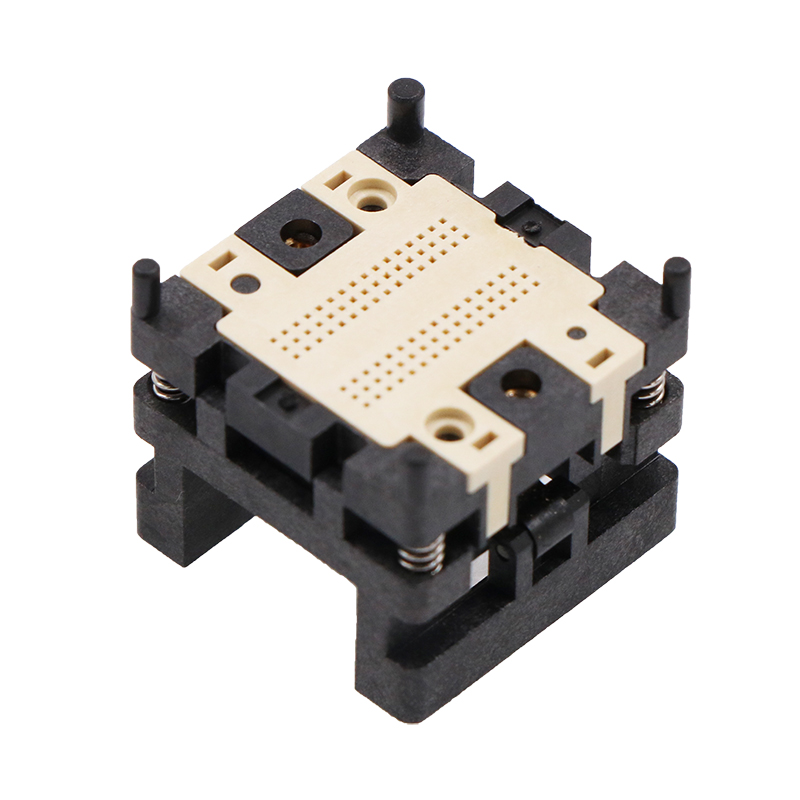

1. DDR芯片测试座

技术优势:

高频支持:BGA78球测试座支持2800MHz以上频率,接触电阻<100mΩ。

兼容性设计:通过更换限位框,适配0.8mm间距的DDR3/DDR4颗粒(宽度≤13mm,长度≤14mm)。

信号完整性:镀金探针(铍铜材质)配合低介电PCB,确保阻抗匹配(±3%)和低插损(<2dB)。

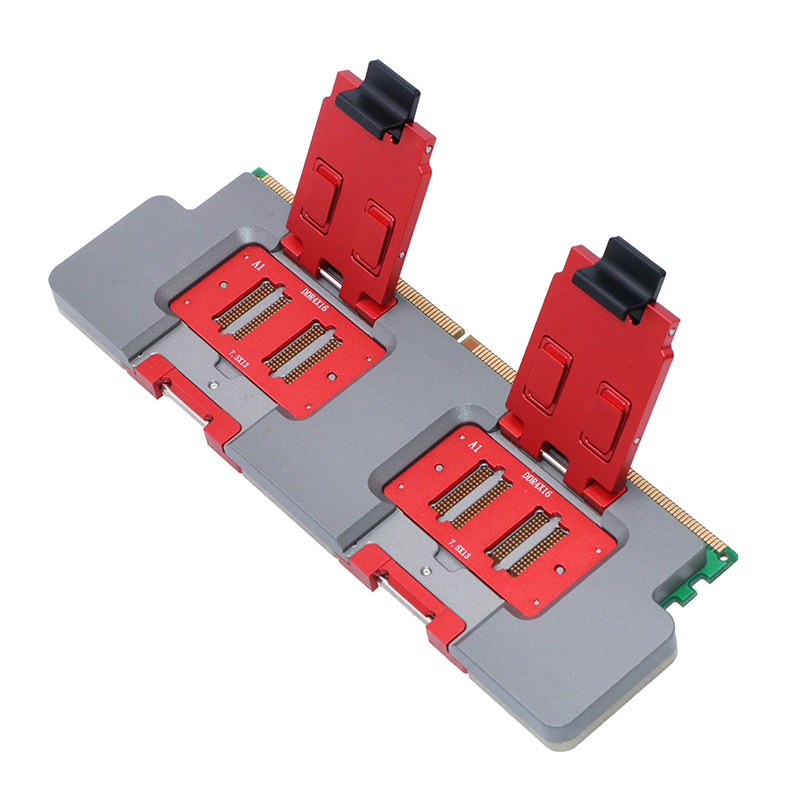

2. DDR芯片老化座

宽温域测试:

温度范围:-65℃~200℃,支持车规级芯片高温反向偏压(HTRB)测试。

多工位并行:64工位老化板实现单日10万颗芯片测试,成本降低30%。 可靠性设计:

抗ESD:±15kV接触放电保护,避免静电损伤。

热管理:导热硅胶和散热片确保温度均匀性±1℃。

3. DDR芯片测试治具

自动化集成:

ATE对接:支持与泰瑞达、爱德万测试机通信,实现全流程自动化。 - 探针寿命:钨铜合金探针插拔寿命>50万次,满足量产需求。

医疗合规性:

生物相容性:材料通过细胞毒性、致敏性测试,支持医疗级传感器芯片灭菌(环氧乙烷耐受)。

四、技术挑战与创新方向

1. 高频信号处理:

100GHz级测试:DDR5 PHY需支持PAM4调制,测试座需集成TDR(时域反射计)实时监测阻抗。

多模态数据融合:NAND闪存同步测试电、热、力参数,测试座需集成补偿算法消除耦合误差。

2. 智能化测试系统:

AI驱动:机器学习分析测试数据,预判芯片寿命和潜在失效模式(如NAND的Vt-shift优化)。

自适应校准:测试座嵌入算法自动调整ODT、驱动强度,适配不同厂商颗粒。

3. 先进封装测试:

3D堆叠:HBM(高带宽内存)测试需支持TSV(硅通孔)互连,探针精度达微米级。

Chiplet架构:多Die协同测试需实现纳秒级时间同步,测试座需集成分布式时钟模块。

鸿怡电子HMILU存储芯片测试座、老化座及治具通过高精度信号完整性设计、宽温域可靠性验证和医疗合规性支持,覆盖DDR存储芯片从设计验证到量产的全流程测试需求。其核心价值不仅在于参数验证,更在于通过早期缺陷筛选和自动化测试,帮助客户提升产品良率、降低成本,并应对高频化、智能化的技术挑战。随着DDR5普及和AI芯片需求增长,测试解决方案的创新将成为产业竞争力的关键。