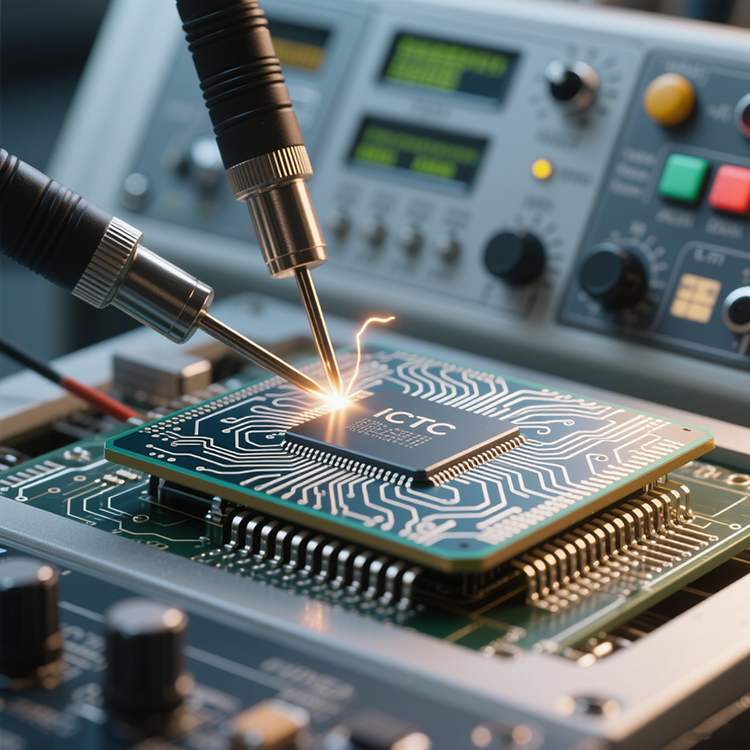

一、ICTC测试的核心框架与测试项 ICTC(In-Circuit Test and Characterization)测试是半导体制造中确保芯片电气性能与功能完整性的核心环节,其测试体系涵盖以下维度:

1. 电气参数测试

静态特性:

I-V曲线扫描:使用半导体参数分析仪(如Keysight B1500)测量漏电流(Ioff)、阈值电压(Vth)等参数,精度需达pA级。例如,车规级芯片要求Ioff在125℃时≤1nA。

接触电阻测试:通过四线开尔文法(Kelvin Probe)测量探针与芯片引脚的接触阻抗,需控制在50mΩ以下。

动态特性:

开关时间测试:利用双脉冲测试电路(DPP)结合示波器(如Tektronix DPO70000),测量GaN器件的上升/下降时间,分辨率需达50ps。

高频响应测试:针对5G射频芯片,使用矢量网络分析仪(如R&S ZNB)在10GHz频段内验证S参数(如S11≤-15dB)。

2. 功能验证测试

逻辑功能测试:

向量测试:通过ATE系统(如泰瑞达J750)加载真值表向量,验证数字IC的逻辑正确性,覆盖率需≥99.9%。

边界扫描测试:遵循IEEE 1149.1标准,使用Boundary-Scan控制器检测PCB互连缺陷,如短路或开路。

协议兼容性测试:

PCIe 5.0合规性:使用NI AWR微波工作室模拟信号完整性,确保眼图模板通过率>95%。

3. 可靠性测试

环境应力测试:

高温反偏(HTOL):在150℃下施加100%额定电压,持续1000小时,漏电流增幅需<20%。

温度循环(TC):在-55℃至125℃间进行500次循环,依据AEC-Q100标准,裂纹扩展需≤5μm。

二、测试方法与设备选型

1. 基础测试工具

参数分析仪:Keysight B1500支持±10kV高压测试,适用于SiC MOSFET的击穿电压(VBR)测量。

示波器:Tektronix DPO70000系列带宽达13GHz,可捕捉GaN器件的开关波形抖动(Jitter)。

ATE系统:泰瑞达J750支持5632测试通道,适合大规模逻辑芯片的并行测试。

2. 高级测试技术

DeltaScan模拟结测试:通过测量芯片引脚间的二极管正向压降,检测焊接缺陷,如虚焊或引脚变形。

热成像分析:使用FLIR A655sc红外相机监测芯片热点,定位热阻异常区域(如Rth(j-c)>1.5K/W)。

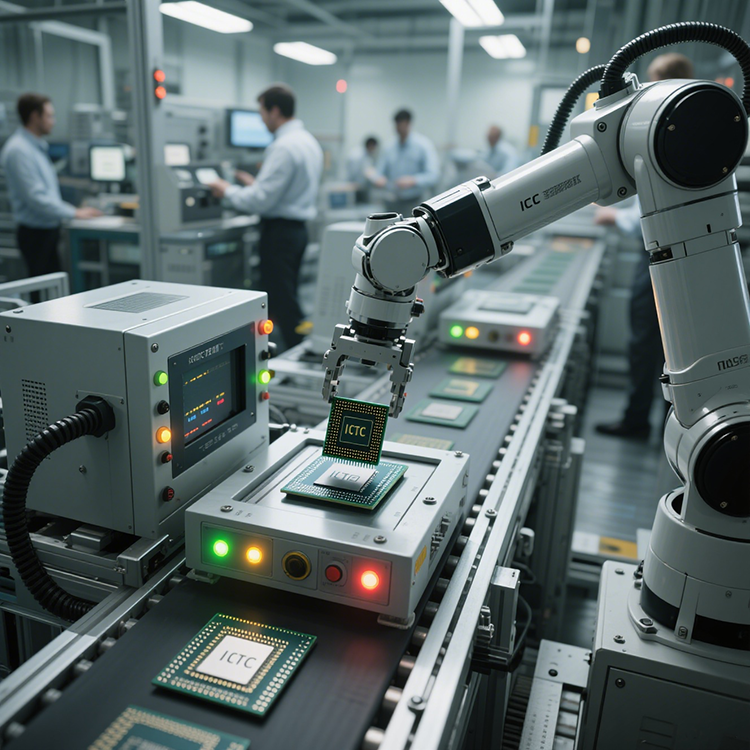

3. 自动化测试流程

测试脚本开发:采用C#或Python编写测试序列,集成探针卡校准、数据采集与报表生成功能。

缺陷分类(DPA):通过机器学习算法分析测试数据,自动识别失效模式(如ESD损伤、氧化层缺陷)。

三、行业标准与合规性要求

1. 通用标准

JEDEC JESD22:定义HTOL、TC等可靠性测试的温度/时间参数,如JESD22-A108规定HTOL测试温度为150℃。

ISO 10474:规范半导体封装的机械性能测试,如BGA焊球剪切力需≥5N。

2. 行业特定标准

汽车电子:

AEC-Q100:要求芯片在-40℃至150℃温度循环下通过500次测试,失效率为0 DPPM。

ISO 26262:针对功能安全(ASIL等级),需在测试中验证故障注入响应时间(≤10μs)。

消费电子:

IEC 62368-1:规定充电器芯片的过压保护阈值(OVP)需≤5.5V。

四、自加热芯片测试座与ICTC测试的协同应用

1. 自加热芯片测试座的技术优势

精准温控:鸿怡BGA132芯片测试座集成PID温控模块,支持-55℃至175℃宽温域调节,精度达±0.5℃。

热响应速度:采用碳纤维基板(CTE=1.2ppm/℃)和导热硅胶垫,可在30秒内升至目标温度,较传统烤箱方案效率提升80%。

多工位并行测试:支持32工位同时加热,配合ATE系统实现批量高温功能测试,单日吞吐量达10万颗。

2. 典型应用场景

高温功能验证:

案例:某汽车ECU芯片在125℃下通过ICT测试,检测到因焊料回流不良导致的间歇性通信中断,不良率从0.3%降至0.01%。

热应力筛选:

方法:在150℃下进行1000次负载循环,筛选出因金属间化合物(IMC)生长导致的接触电阻上升(ΔR>10%)。

宽温域信号完整性测试:

设备:鸿怡QFN测试座支持-40℃至125℃测试,配合R&S ZNB网络分析仪验证射频芯片的S参数漂移(ΔS11≤0.5dB)。

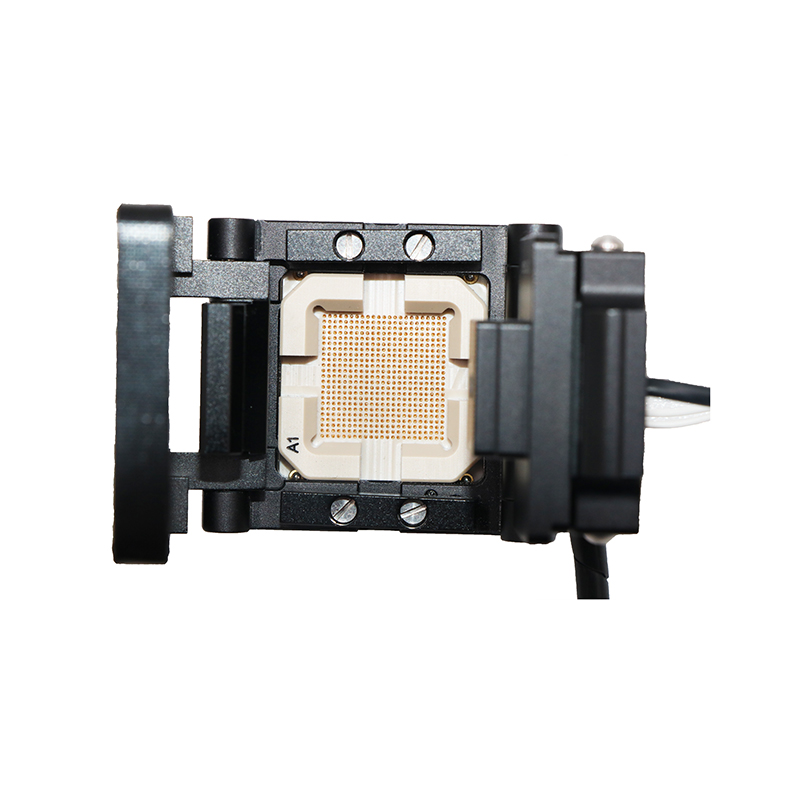

3. 鸿怡芯片自加热测试座的核心设计

探针技术:

双头铍铜探针:接触电阻<50mΩ,插拔寿命>15万次,适用于BGA封装的密集引脚测试。

开尔文探针结构:四线制设计消除接触电阻干扰,适合微欧级导通电阻(RDS(on))测量。

热管理设计:

嵌入式热电偶:实时监测芯片结温,结合Peltier制冷器实现动态温度补偿(±0.2℃)。

散热鳍片:铝制外壳表面积达2000mm²,可在100A负载下将温升控制在40℃以内。

测试流程优化与成本控制

1. 测试效率提升

并行测试架构:采用多工位测试座(如16工位)和分时复用技术,将测试时间从2分钟/颗降至15秒/颗。

自动化校准:通过ATE系统自动完成探针卡偏移补偿(±5μm),减少人工干预时间。

2. 成本优化策略

模块化设计:鸿怡芯片测试座支持探针板快速更换(10分钟内),降低不同封装类型的芯片测试夹具成本。

数据分析:通过历史测试数据预测探针磨损周期,将探针更换频率从5万次延长至10万次。

五、未来发展趋势

1. 技术创新方向

高频测试:开发120GHz同轴探针,支持太赫兹芯片的信号完整性测试(插损<3dB)。

AI驱动测试:利用机器学习算法分析测试数据,动态调整测试参数(如电压阈值),提升缺陷检出率。

三维封装适配:研发垂直探针阵列,支持3D IC堆叠结构的层间互连测试。

2. 行业整合趋势

测试设备国产化:鸿怡电子等本土厂商通过技术突破,将芯片测试座成本降至进口产品的1/3,推动国产替代进程。

测试服务专业化:第三方实验室(如CTI华测检测)提供HTOL、HAST等一站式可靠性测试服务,缩短产品上市周期。

ICTC测试通过电气参数验证、功能测试与可靠性评估,确保芯片在复杂工况下的稳定性。自加热测试座(如鸿怡BGA132测试座)通过宽温域控制、高精度对位与高效散热设计,成为高温测试的关键支撑。随着半导体技术向高频、高压、微型化发展,测试设备需进一步提升信号完整性、热管理与自动化水平,以应对SiC/GaN器件、3D IC等新兴领域的测试挑战。