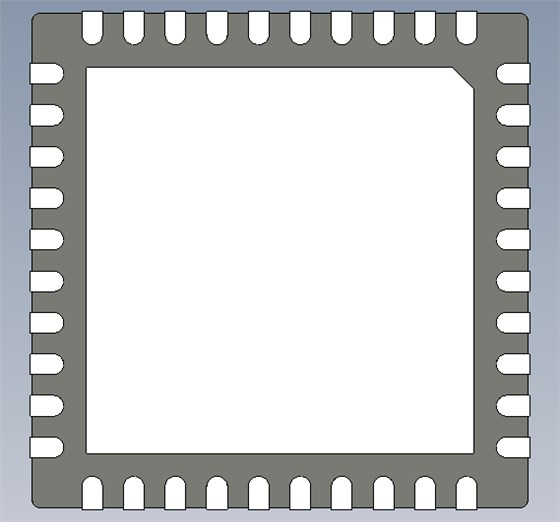

QFN封装芯片的特点与适用场景

QFN(Quad Flat No-lead)封装凭借无引脚设计、底部大面积裸露焊盘,成为高密度小型化电子产品的优选方案。其核心优势包括:

1. 体积轻薄:封装高度低至0.8mm,适用于智能穿戴、微型传感器等空间敏感场景;

2. 散热高效:底部金属焊盘直接连接PCB,热阻降低30%-50%,满足5G基站、车载ECU等高功耗需求;

3. 电性能优越:短引脚结构减少寄生电感,适配高频通信芯片及高速数据处理模块。

主要应用于消费电子(如手机射频芯片)、工业控制(MCU模块)及新能源汽车(BMS控制芯片)三大领域。

QFN芯片测试的核心挑战与方法

测试难点在于:

焊盘接触稳定性:底部焊盘无外延引脚,需精准对位;

散热干扰控制:测试时需模拟真实散热条件;

高频信号完整性:阻抗匹配要求±5%以内。

主流测试方案:

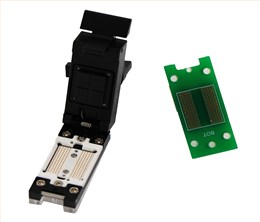

1.功能测试(FT):通过测试座接入ATE设备,验证I/O端口时序与功耗;

2. 在线测试(ICT):检测焊接后短路/开路缺陷;

3. 老化测试(Burn-in):85℃高温下持续运行48小时筛选早期失效品。

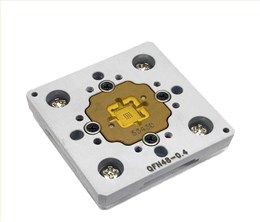

QFN测试座关键技术参数

| 参数类别 | 技术指标要求 | 实现方案 |

|----------------|-----------------------|-------------------------|

| 接触阻抗 | ≤30mΩ(DC 1A) | 镀金微弹簧探针 |

| 耐压值 | AC 500V@1分钟 | 陶瓷绝缘基板 |

| 插拔寿命 | ≥10万次 | 钨钢导向柱+自清洁结构 |

| 温控范围 | -40℃~+175℃ | 内置热电偶+导热硅胶垫 |

核心技术创新点:

三阶定位系统:精密导柱+浮动探针+真空吸附,实现±5μm对位精度;

混合信号测试通道:支持最高56Gbps高速差分信号传输;

模块化设计:10分钟内完成测试座规格切换。

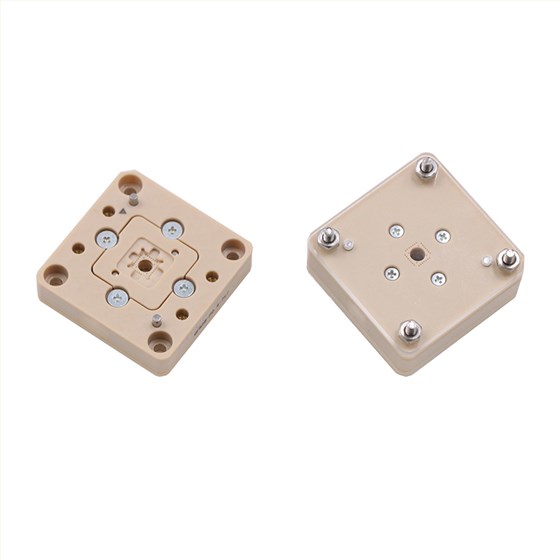

QFN芯片测试座/老化座/烧录座的关键应用

1. 量产测试座

案例:某品牌TWS耳机主控芯片测试

配置:256针全矩阵探针阵列,支持并行测试8颗芯片

效率:单日完成20万颗芯片筛选,不良品检出率>99.97%

2. 高温老化座

设计:集成PID温控模块,支持150℃持续运行

应用:汽车ECU芯片批次老化测试,故障率从500ppm降至50ppm

3. 自动化烧录座

创新:集成ISP编程接口,支持JTAG/SWD双协议

流程:自动校准→程序烧录→CRC校验→分Bin收集,良率提升至99.8%

行业发展趋势

随着QFN封装向0.35mm间距演进,芯片测试座技术正朝以下方向突破:

微间距探针:直径0.12mm钨铜合金探针量产应用;

智能测试系统:集成AI算法实时诊断接触不良问题;

多物理场耦合:同步监控电-热-力参数,构建芯片可靠性数字孪生模型。

新能源汽车车规芯片DFN封装MOS场效应管\大功率管 测试座_PDFN芯片老化座

新能源汽车车规芯片DFN封装MOS场效应管\大功率管 测试座_PDFN芯片老化座 GDDR5探针测试座 BGA178测试架 夹具 工装 2.8GHz高频测试

GDDR5探针测试座 BGA178测试架 夹具 工装 2.8GHz高频测试 QFN测试烧录座 QFN自动设备用ATE测试座 烧录座芯片转换座

QFN测试烧录座 QFN自动设备用ATE测试座 烧录座芯片转换座 大电流弹片微针模组

大电流弹片微针模组