一、国产DDR系列存储芯片的种类与技术演进

国产DDR存储芯片以长鑫存储(CXMT)为代表,已实现从DDR4到DDR5的全系列覆盖。DDR4采用19nm工艺,单颗芯片容量达16Gb,支持1.2V电压,最高速率3200MT/s,主要应用于消费级PC和数据中心。

2025年,长鑫存储的DDR5良率已突破80%,采用17nm工艺,支持400MHz基频和PAM4调制,单颗芯片容量提升至16Gb,速率达6400MT/s,电压降至1.1V,同时引入双32位独立子通道设计,带宽较DDR4提升50%以上。

配套的思远半导体DDR5 PMIC(如SY5888)已量产,支持超频至8000Mbps,并集成3个高效降压转换器,为国产DDR5提供完整电源解决方案。

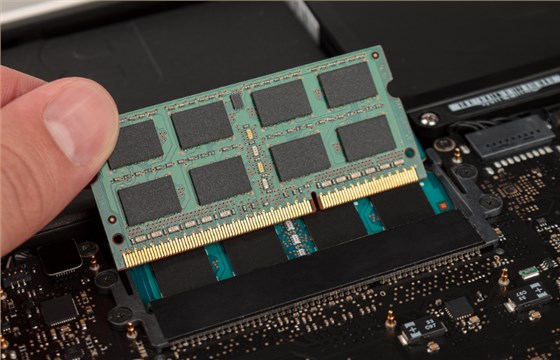

二、DDR存储芯片的封装形式与引脚数

1.封装形式

TSOP(薄型小外形封装):早期DDR1/DDR2采用,引脚分布于芯片两侧,成本低但散热和高频性能有限,适用于低功耗场景。

FBGA(细间距球栅阵列封装):DDR3/DDR4/DDR5主流封装,引脚以焊球阵列分布于芯片底部,引脚密度高(如DDR4的284针),散热和信号完整性显著优于TSOP,支持更高频率(如DDR5的6400MT/s)。 3D堆叠封装:通过TSV(硅穿孔)技术实现多Die堆叠,提升容量(如长鑫存储计划量产HBM2),但目前主要用于高端市场。

2.引脚数与防呆设计

DDR1:184针,缺口位于中部,支持2.5V电压。

DDR2:240针,缺口偏左,电压1.8V,采用FBGA封装。

DDR3:240针,缺口偏右,电压1.5V,FBGA封装成为主流。

DDR4:284针,缺口位置进一步右移,电压1.2V,支持更高密度集成。

DDR5:288针,缺口偏左,物理接口与DDR4不兼容,引入PMIC集成设计,单条容量达128GB。

三、DDR存储芯片的测试方法与关键技术

1.功能测试

读写验证:通过March C算法检测存储单元故障,验证数据一致性。

地址映射测试:遍历所有地址线,确保译码逻辑正确,无重叠或遗漏。

电源完整性测试:测量静态电流(ISB≤10μA)和动态电流(ICC≤50mA),验证功耗是否符合JEDEC标准。

2.性能测试

带宽与延迟测试:通过连续读写计算实际带宽(DDR5可达44800MB/s),测量读命令到数据返回的延迟(TAA≤12ns)。

信号完整性测试:使用示波器生成眼图,分析抖动、噪声裕量,确保眼宽和眼高满足协议要求。

SSN(同时切换噪声)测试:模拟多信号同时翻转,验证电源/地网络抗干扰能力,鸿怡芯片测试座通过差分探针设计将串扰抑制至-30dB以下。

3.可靠性测试

HTOL(高温工作寿命测试):在125℃下运行1000小时,监测漏电流(≤10μA)和刷新间隔(64ms周期)。

温度循环测试:在-55℃~175℃范围内进行1000次循环,验证接触电阻波动<5mΩ。

抗辐射测试:针对军品场景,鸿怡芯片测试夹具通过重离子加速器接口监测软错误率(SER),探针采用“金-钯-镍”复合镀层,寿命达80万次

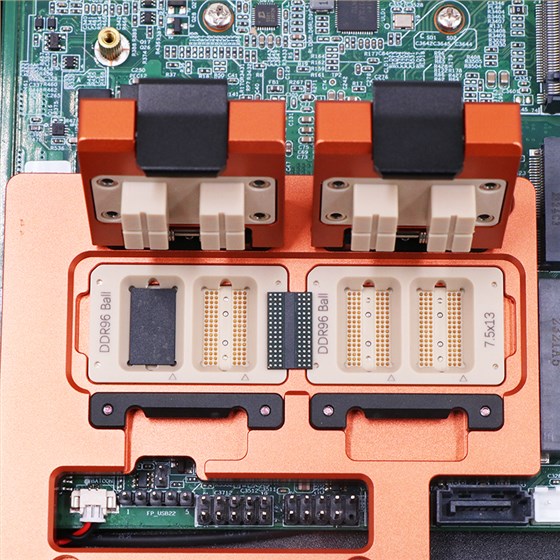

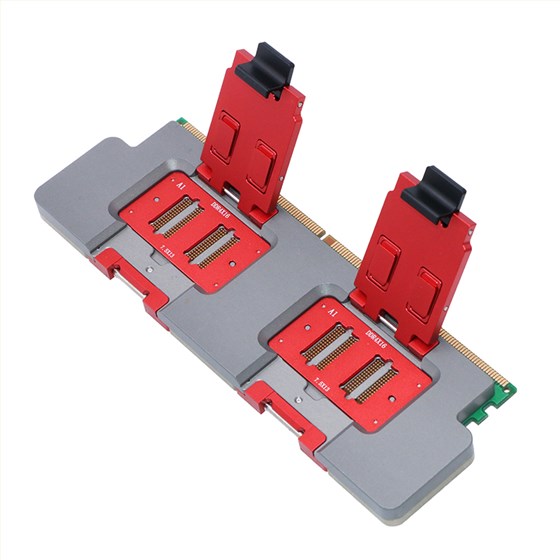

四、鸿怡DDR测试解决方案关键应用

1.测试座技术创新

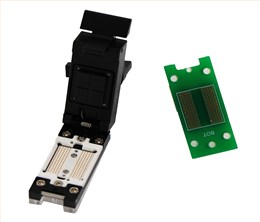

高精度信号完整性:BGA测试座采用双曲面接触头设计,接触电阻<20mΩ,支持0.35mm焊球间距检测,适配DDR4/DDR5的FBGA封装。

高频与宽温域支持:27GHz高频测试座(如BGA16pin)用于5G基带芯片测试,单日产能10万颗;宽温域老化座集成热电偶,实时监控结温,支持-55℃~175℃环境下的稳定性验证。

AI驱动校准:通过机器学习动态补偿探针磨损,误判率降低至0.01%,并支持自动生成测试报告。

2.DDR芯片老化座与夹具治具

多场景适配:GDDR测试治具支持10GHz高频颗粒,可同时测试4颗芯片,冷却系统确保稳定性;DDR芯片测试夹具(如HMILU-DDR96pin)采用合金翻盖设计,支持0.8mm间距,双工位设计提升量产效率30%以上。

军品级可靠性:国某科技大学项目中,鸿怡电子的抗辐照夹具通过MIL-STD-810G振动测试和IP67防护认证,电磁屏蔽性能满足GJB151B-2013标准,价格仅为进口设备的1/3。

3.全流程测试支持从设计到量产:

芯片测试座覆盖晶圆级测试(飞针扫描)、封装后测试(功能/性能验证)及老化测试筛选,支持JEDEC JESD79-5C(DDR5)等标准。

定制化服务:根据客户主板布局设计治具,如针对DDR5的288针接口优化探针排列,确保信号传输延迟<0.5ps。

未来,随着3D堆叠、HBM等技术的引入,测试设备需进一步提升高频信号处理(如100GHz)和高密度集成能力,以满足AI、数据中心等场景的需求。国产替代的深化将推动存储产业链的全面升级,助力中国半导体产业迈向高端化。

新能源汽车车规芯片DFN封装MOS场效应管\大功率管 测试座_PDFN芯片老化座

新能源汽车车规芯片DFN封装MOS场效应管\大功率管 测试座_PDFN芯片老化座 GDDR5探针测试座 BGA178测试架 夹具 工装 2.8GHz高频测试

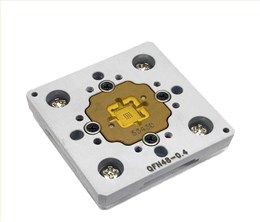

GDDR5探针测试座 BGA178测试架 夹具 工装 2.8GHz高频测试 QFN测试烧录座 QFN自动设备用ATE测试座 烧录座芯片转换座

QFN测试烧录座 QFN自动设备用ATE测试座 烧录座芯片转换座 大电流弹片微针模组

大电流弹片微针模组